# Unified Design Flow for Silicon Photonics

#### **Outline**

- Silicon photonics flow introduction

- Photonic IC circuit simulation with INTERCONNECT

- PDK driven flow with Pyxis and Calibre

- Design capture and implementation with Pyxis

- PDK driven flow with Pyxis and Calibre (continued)

- → Physical verification Calibre

- → PhoeniX Collaboration

- Photonics + CMOS

- Available PDKs

#### What's new?

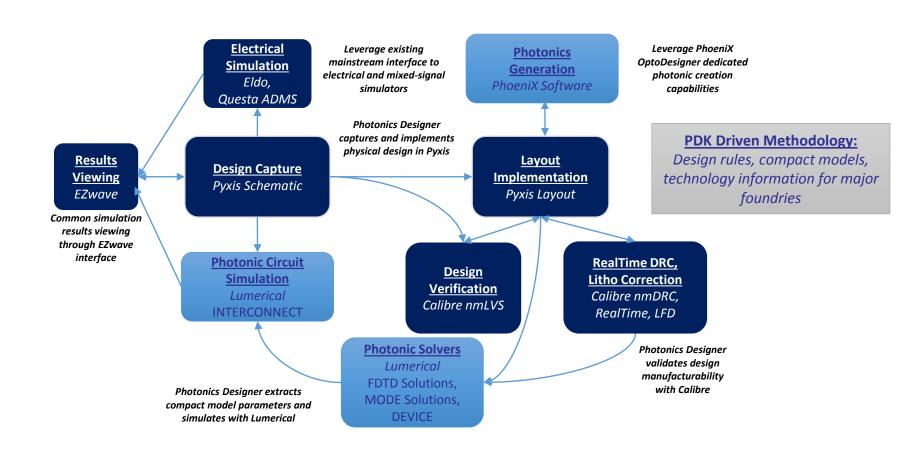

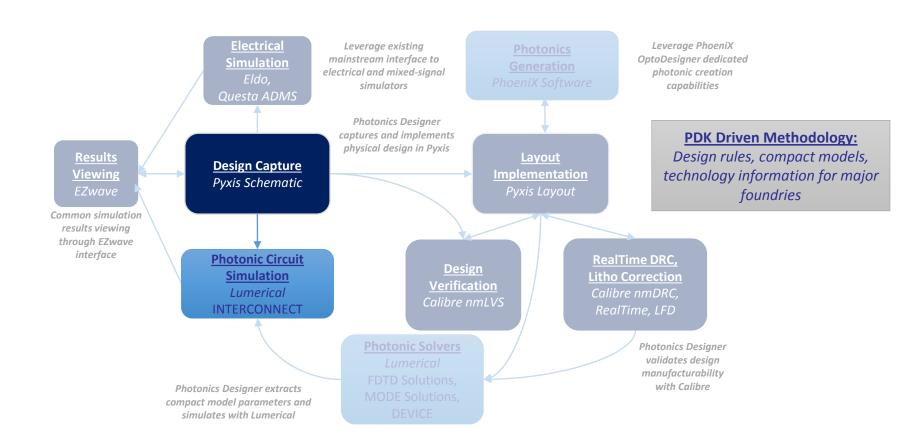

A complete design flow for silicon photonics

### SILICON PHOTONICS FLOW INTRODUCTION

### Design flow for silicon photonics

A generic, non-proprietary silicon photonics design kit is available for download at <a href="http://www.siepic.ubc.ca/GSiP">http://www.siepic.ubc.ca/GSiP</a>

### Design flow for silicon photonics

A generic, non-proprietary silicon photonics design kit is available for download at <a href="http://www.siepic.ubc.ca/GSiP">http://www.siepic.ubc.ca/GSiP</a>

A complete design flow for silicon photonics

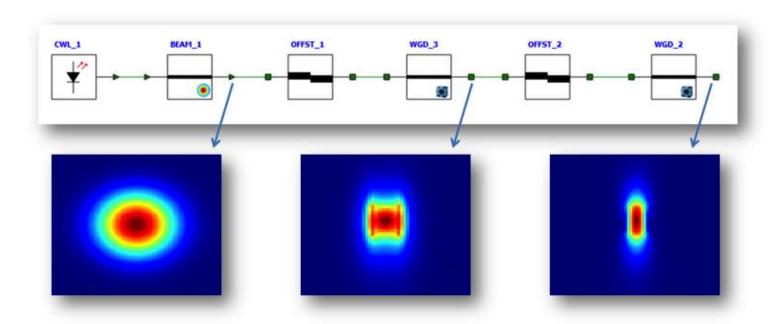

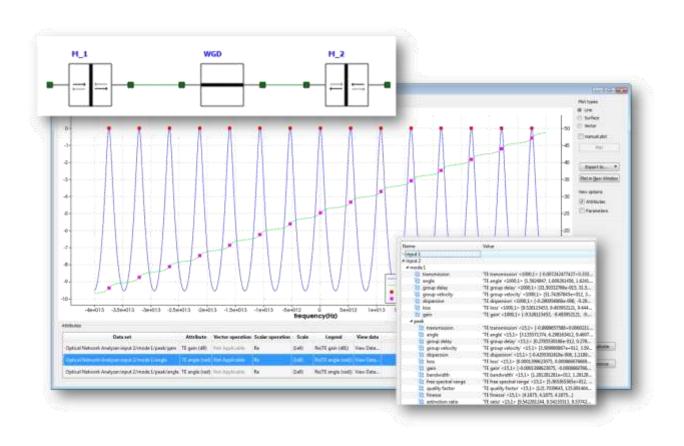

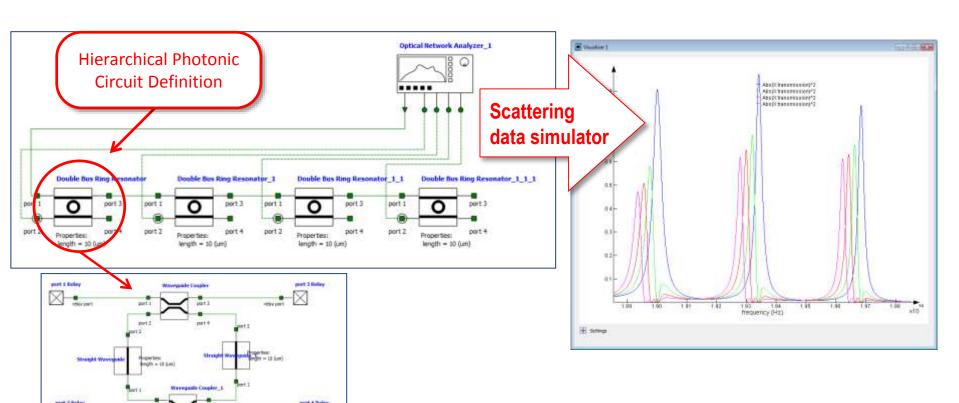

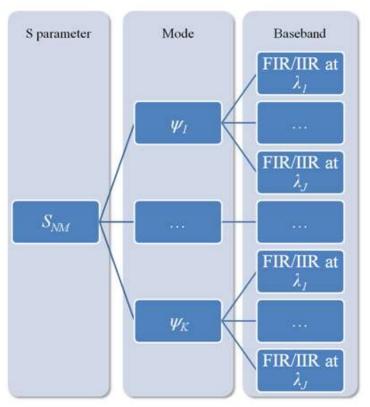

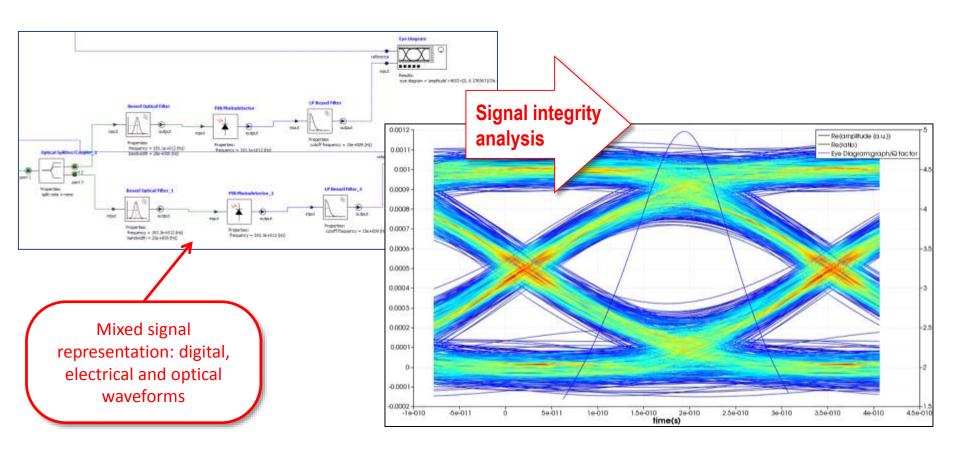

## PHOTONIC IC CIRCUIT SIMULATION WITH INTERCONNECT

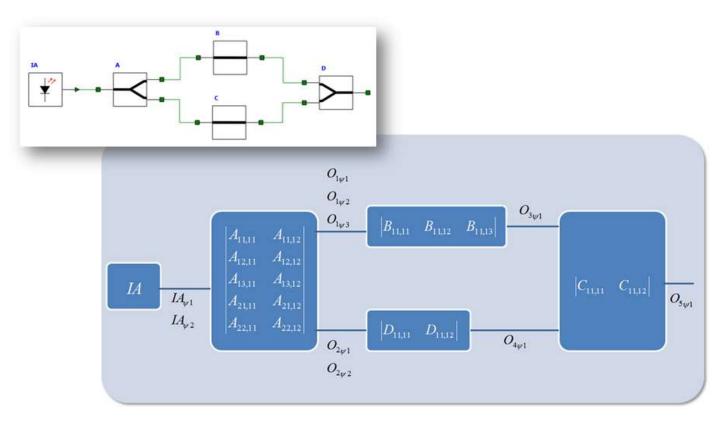

- Frequency domain simulation: Scattering data analysis

- Supports bidirectional, multimode and multichannel optical circuits

- Frequency domain simulation: Scattering data analysis

- → Supports bidirectional, multimode and multichannel optical circuits

- Frequency domain simulation: Scattering data analysis

- Supports bidirectional, multimode and multichannel optical circuits

- Frequency domain simulation: Scattering data analysis

- Supports bidirectional, multimode and multichannel optical circuits

- Time domain simulation: Transient analysis

- Supports bidirectional, multimode and multichannel optical circuits

- Time domain simulation: Transient analysis

- Supports bidirectional, multimode and multichannel optical circuits

A complete design flow for silicon photonics

#### DRIVING INTERCONNECT FROM PYXIS

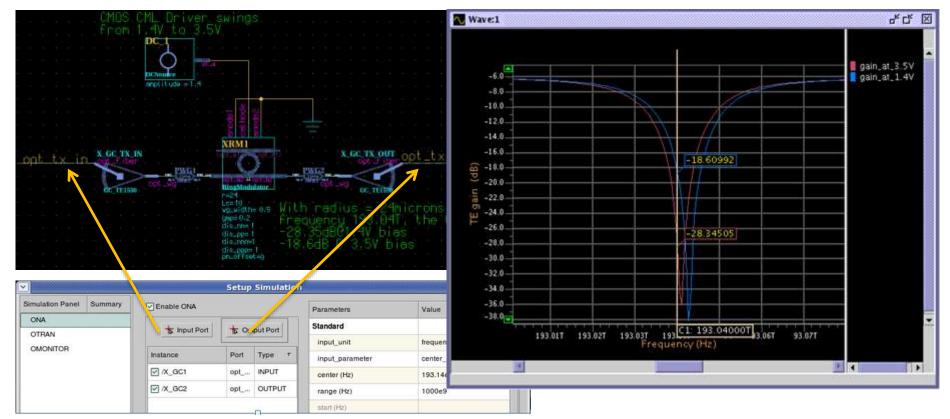

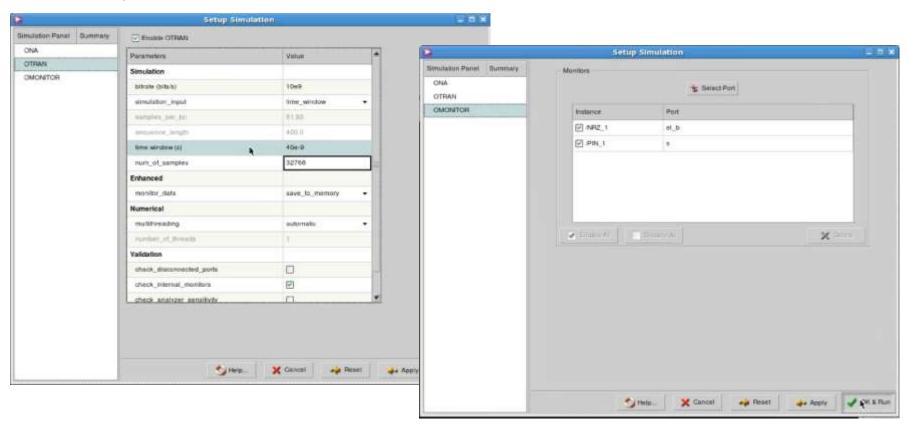

## **Driving INTERCONNECT from Pyxis**

- Frequency domain spectral response

- ☐ Interactively setup sizing and DC biasing of modulators in Pyxis with Lumerical INTERCONNECT ONA simulation

- ✓ View results in Mentor's EZwave results viewer

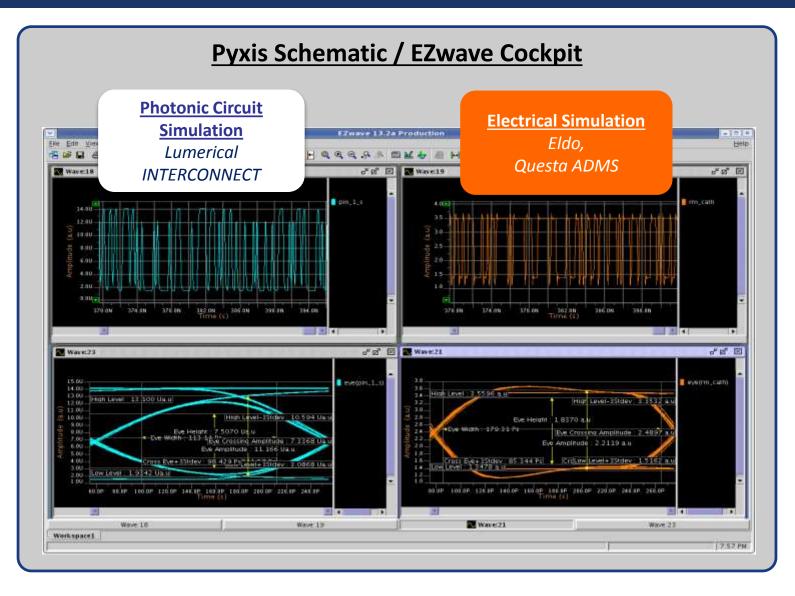

## Driving INTERCONNECT from Pyxis

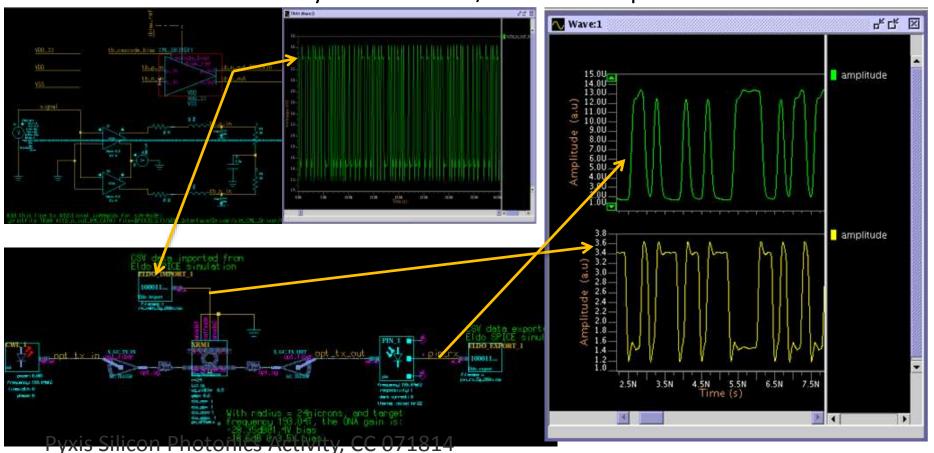

- System level time domain simulation

- ✓ User remains in Pyxis Schematic / EZwave cockpit for electrical and optical simulation

A complete design flow for silicon photonics

#### PDK DRIVEN FLOW WITH PYXIS AND CALIBRE

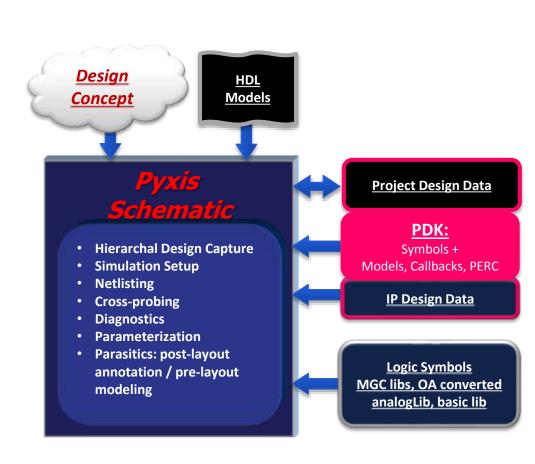

## Design Creation/Capture

- A complete environment to capture and simulate IC design concepts

- Supports Mixed Signal Language Modeling Formats

- ∇HDL, Verilog,

VHDL-AMS, Verilog-AMS

- → SPICE, VerilogA

- Integrated simulation flow supports fast iterations and analysis

- PDK driven to enable full design flow from schematic capture to post-layout simulation

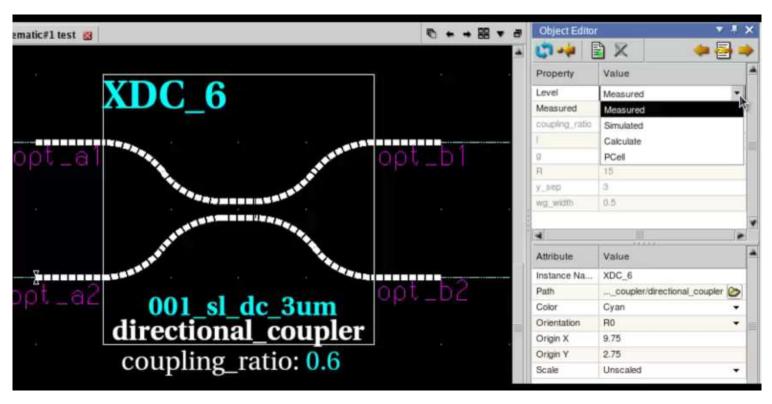

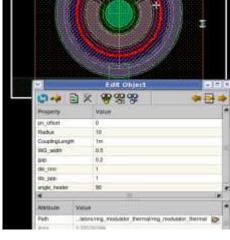

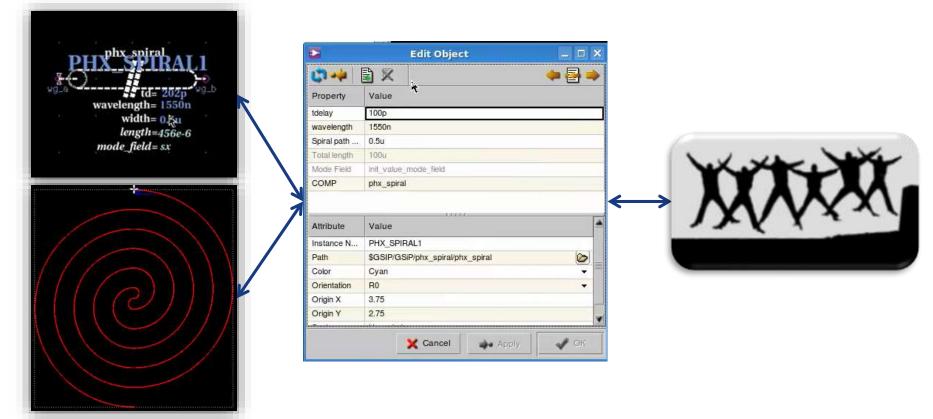

## Design Intent Based Property Editing

- Pyxis enables PDKs to be developed to assist to enter design parameters by system properties, not geometries

- Prototype Preview:

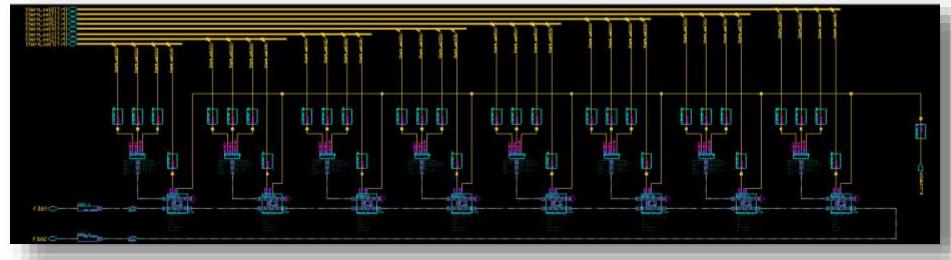

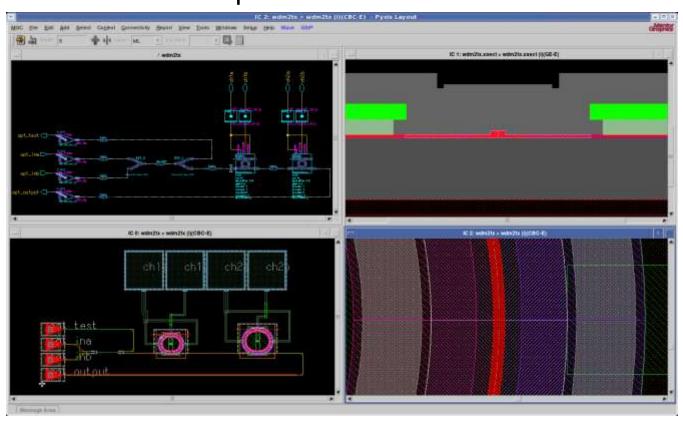

## Silicon Photonics Schematic (with Actives)

- Photonic and electrical connections automatically detected

- PDK supplied schematic checks for photonic connections

- Schematic connectivity drives layout directly

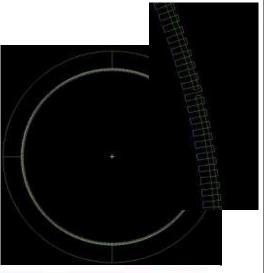

## Pyxis Framework Supports All Angle Editing

- Pyxis Layout has been designed to support non-orthogonal layout

- Can add and rotate objects (paths, shapes, instances, devices) at any angle

- Current uses:

- **7** MEMs

- 7 TFT

- Custom Power Devices

- → Silicon Photonics

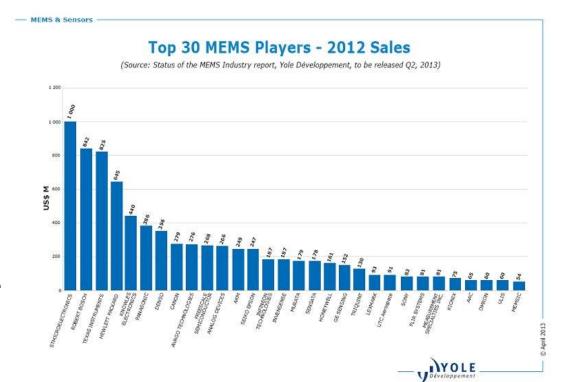

## MEMS Design Implementation Pyxis Layout

- Pyxis Layout used by five of the top ten suppliers

- Design types

- **⊿** Inkjets

- Microphones

- **↗** Accelerometers

- → Pressure sensor

- Leverages Pyxis Layout's unique capabilities in curvilinear applications

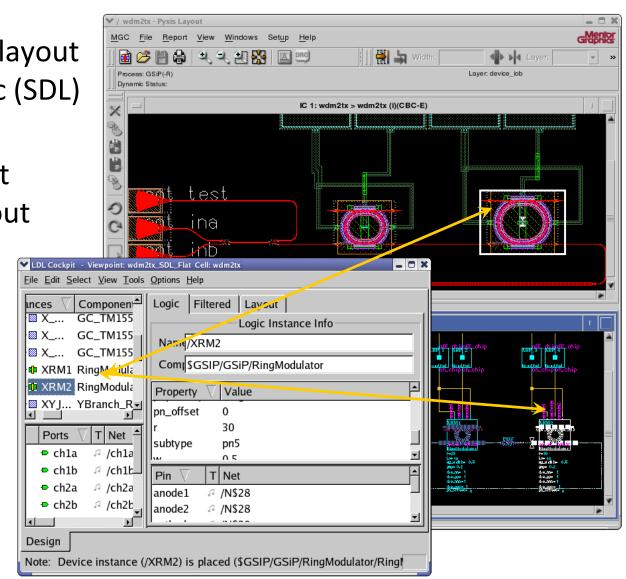

## Schematic/Connectivity Driven layout

- Connectivity-driven layout from both schematic (SDL) and netlist

- PCell support for fast foundry-correct layout

- Interactive connectivity driven routing for fast interconnect with waveguides or metal

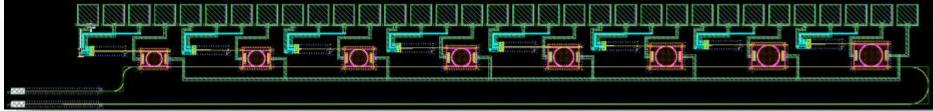

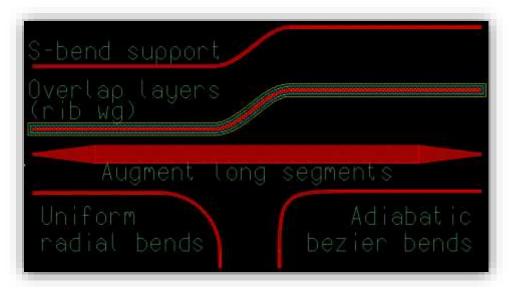

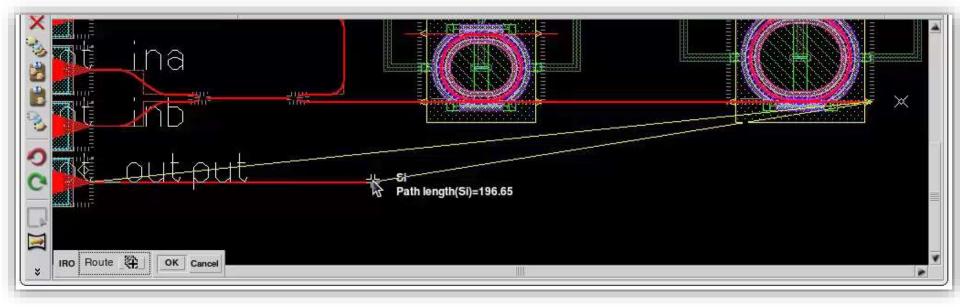

## Schematic/Connectivity Driven layout

- Connectivity waveguide routing implemented using IRoute interactive router

- Supports overlap layers

- Keeps track of waveguide length and other key parameters for simulation

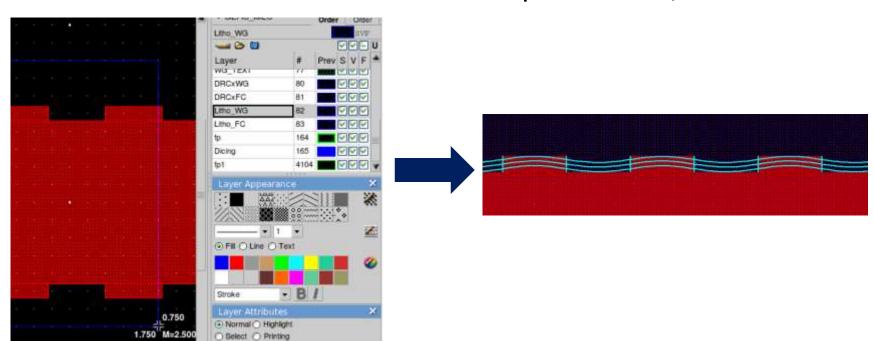

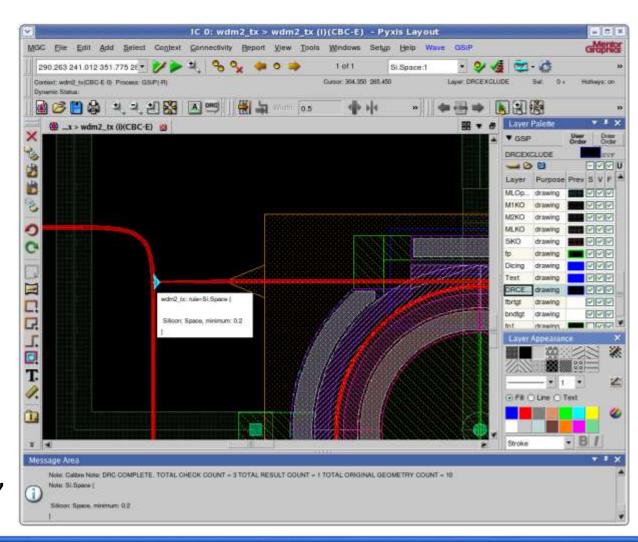

## Physical Verification for Silicon Photonics Calibre Verification Platform

- Reducing "False" DRC Errors

- RealTime design integration

- Recognize & extract photonic devices

- Open detection & short isolation

- Wave guide curvature verification

- Lithographic Simulation

Drawn

Litho-simulated

## **Lithography Simulation**

- Ideal sharp edges of grating will smooth due to lithography resolution

- This change in geometry will affect component attributes

- Run a Calibre LFD lithography simulation directly in Pyxis Layout window with Calibre RealTime or on exported GDS/Oasis data

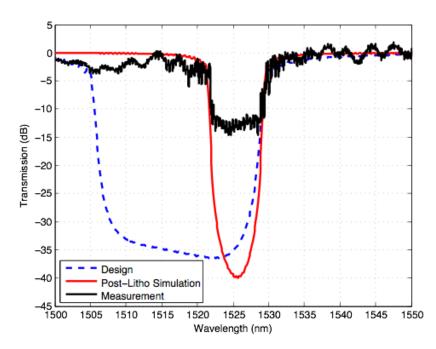

#### Simulation of Lithography Effects

- Comparison of device designed with 40 nm square corrugations

- Litho Correction and FDTD Solutions simulations match experimental Bragg bandwidth

Xu Wang, et al., "Lithography Simulation for the Fabrication of Silicon Photonic Devices with Deep-Ultraviolet Lithography", IEEE GFP, 2012

Original

Litho simulated

## Calibre RealTime Interface

- Sign-off quality DRC as you edit, using standard Calibre decks

- Setup and Manage DRC Checking Recipes

- Navigate and fix errors in the design tool

- Supports Calibre

Interactive LVS, DRC,

xRC/ xACT and PERC

Real-time signoff DRC means better layout in less time

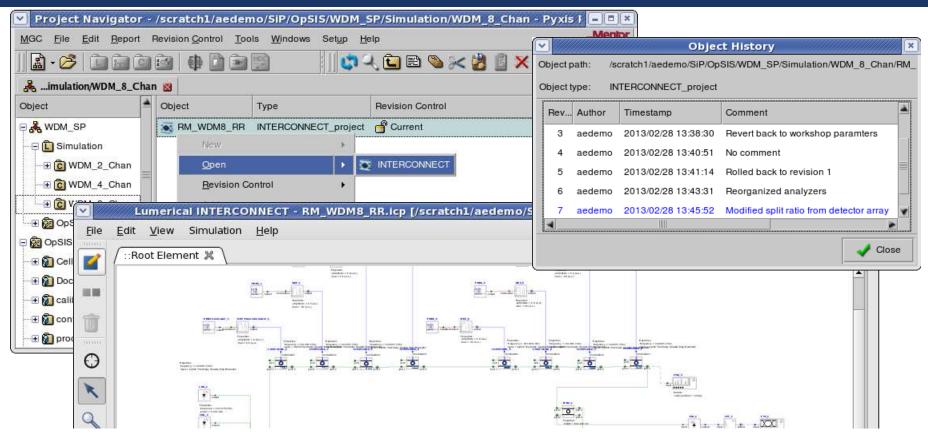

## The Pyxis Framework Data Management with Revision Control

Pyxis Project Manager can easily manage 3rd party data and tool invocation with ClioSoft SOS EDA style revision control

## Enhancing Methodology PhoeniX Collaboration

- Using CMS Call backs for D.I.B. property editing

- → Designer enters time delay, width and desired wavelength

- PhoeniX returns implementation parameters to schematic and layout

- PhoeniX creates PCell enabling full Schematic Driven Layout

A complete design flow for silicon photonics

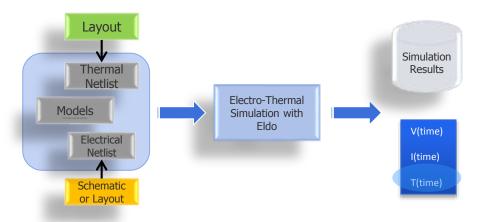

PHOTONICS + CMOS

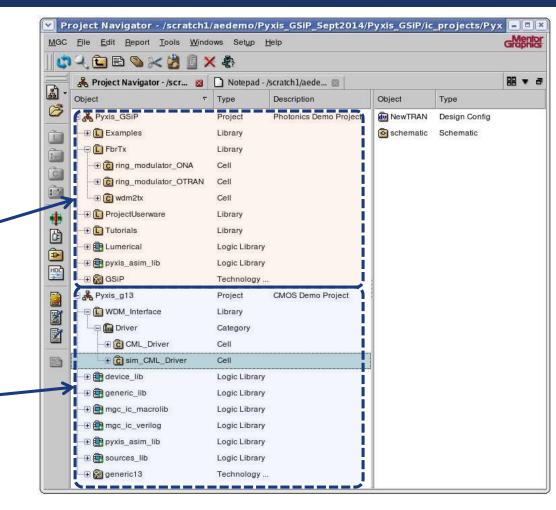

#### Common data management environment

- Pyxis Project Manager enables multi-project viewing

- Silicon Photonics design project

- **⊅** GSiP PDK

- CMOS design project

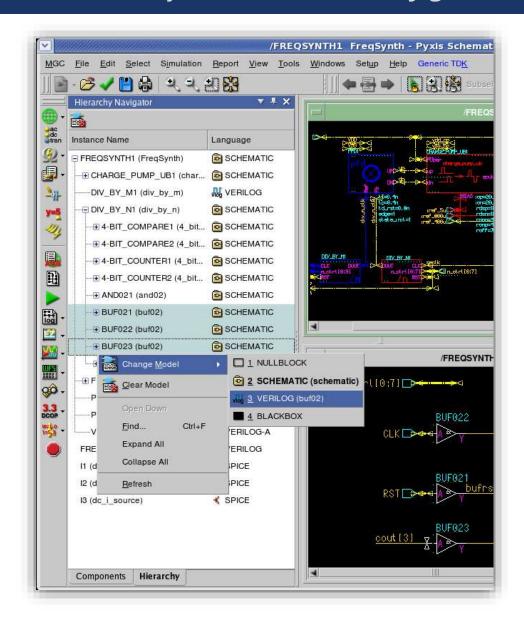

#### Pyxis integration to AMS products

#### Pyxis Schematic

Schematic Capture Environment

#### **EZwave**

Waveform Viewer and Analyzer

AMS Results Browser

**ASCII Results Viewing**

#### Questa ADMS

Mixed Signal Simulator for Full-chip Verification

#### Eldo Classic

Accurate SPICE Simulator for Cell-Characterization and Small IP Verification

#### Eldo Premier

Accurate Faster-SPICE Simulator for Large IP Verification

#### ADIT

Fast-SPICE Simulator for Full-Chip Verification

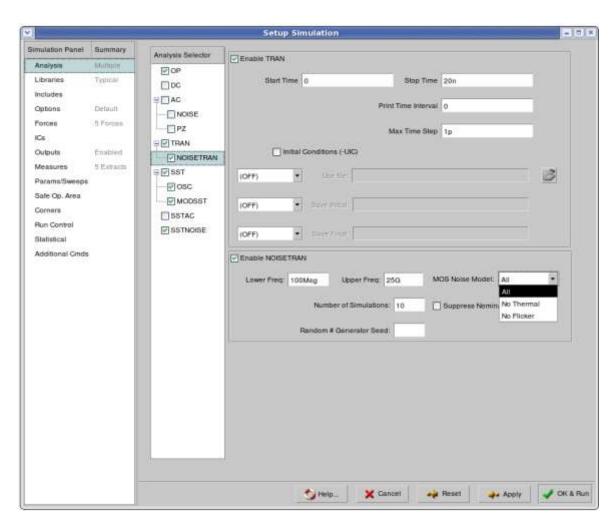

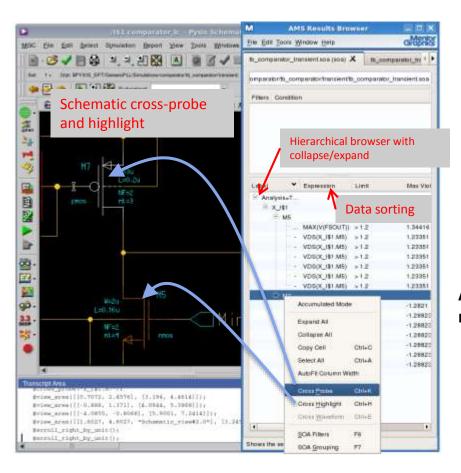

#### Comprehensive simulation setup

Setup and configure simulation analyses available with

the simulator

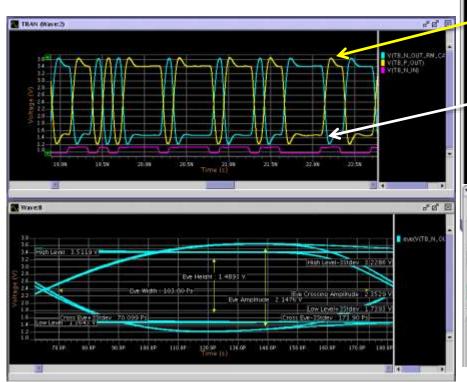

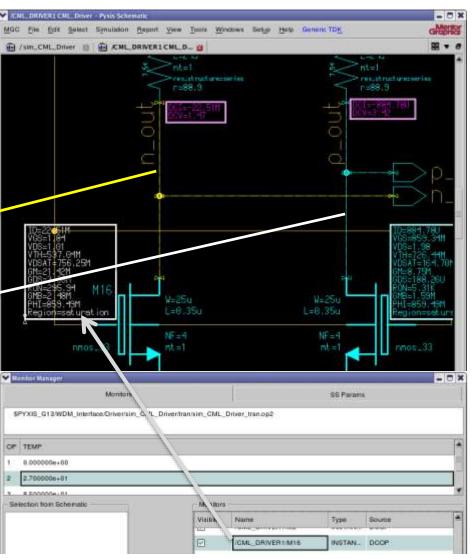

#### Post-simulation results analysis

- Cross-probe to EZwave with matching color

- Annotate simulation values directly to schematic

#### Hierarchy based model configuration

- Navigate by design hierarchy or by component listing

- Bidirectional cross selection between hierarchy navigator and schematic

- Configure models for multiple selected instances

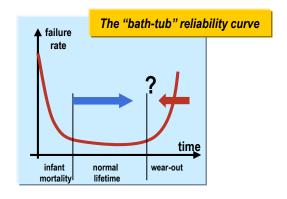

#### **Diagnostic Simulation**

Aging analysis: hot carrier and NBTI analysis -user definable models

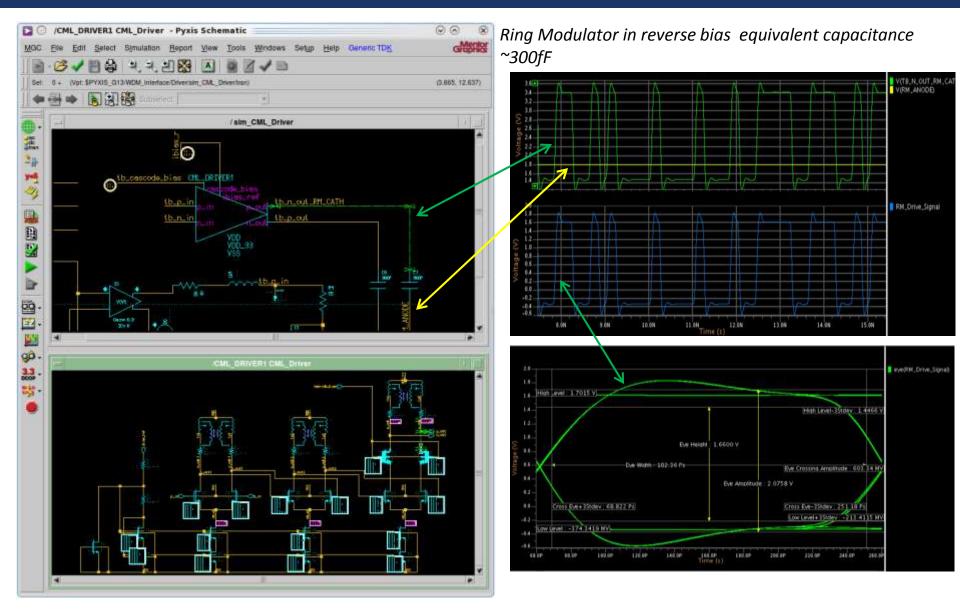

## Photonics + CMOS Generic13 CML Driver Example

## **Driving INTERCONNECT from Pyxis**

- System level time domain simulation

- User remains in Pyxis Schematic / EZwave cockpit for electrical and

#### **Unified Post-Simulation Analysis in EZwave**

A complete design flow for silicon photonics

### **AVAILABLE PROCESS DESIGN KITS**

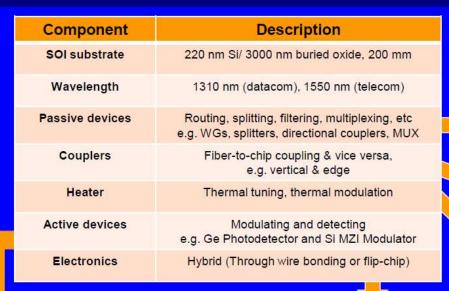

### PDKs for Silicon Photonics

IME and IMEC Foundry PDKs (Available through CMC/Si-EPIC)

"designed to train undergraduate and graduate students and postdoctoral fellows across Canada

Si-EPIC in the new discipline of ... (ICT)

systems that involves miniaturization of optical components onto silicon chips"

http://siepic.ubc.ca

Working directly with A\*STAR IME to replace OpSIS offering

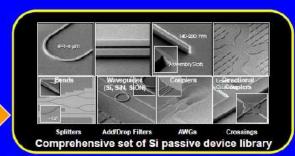

#### IME

- Passives

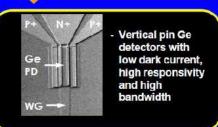

- Modulators

- Detectors

- Edge / grating coupling

IMEC (PDK in development)

imec 7 Basic PDK available – working on full flow functionality

### PDKs for Silicon Photonics

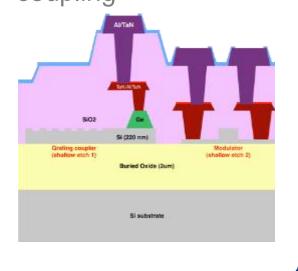

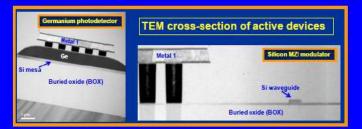

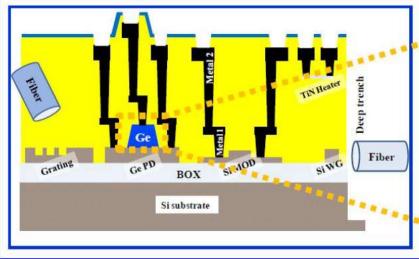

#### **IME's Silicon Photonics Process Platform**

#### **Process overview**

- o 220nm Si/3 μm buried oxide (BOX) SOI

- Front-end process

- 2 Si partial etches, 1 full etch to BOX

- 6 implants for active devices

- Ge epitaxial growth

- Backend process

- 2 Al metal layers with W via plugs, TiN heater layer between the 2 metal layers

- 120 μm deep Si trench

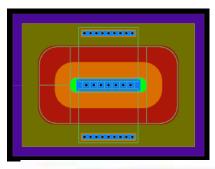

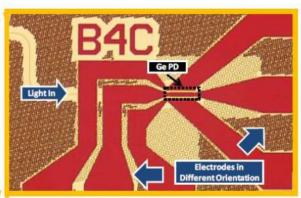

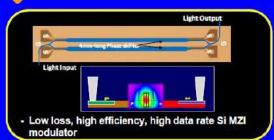

Photonic devices includes but not limited to Si passives (couplers, waveguides, crossings, splitters, bends, etc..), Si MZI MOD, Ge pin PD, and TiN heater

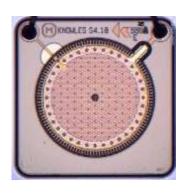

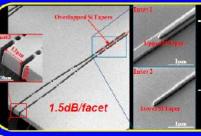

### PDKs for Silicon Photonics

#### **IME's Silicon Photonics Technology Overview**

- Cantilevered mode-size convertor, Si nanotaper, Si 1-D, 2-D gratings - Low loss, high alignment tolerance

- High-Efficiency Integrated TO device for tuning, modulation of Switches, ring resonators;

- Thermal Isolation

- e.g., 2x2 MZI

## NDA neutral GSiP PDK with tutorials Available now!

- The Pyxis Wave reference packages provides extended features for Silicon Photonics PDK development

- Supports tiered custom PCell loading

- Waveguide routing enables full SDL flow

Contains NDA neutral Silicon Photonics PDK created by University of British Columbia

## **THANK YOU!**